继CS439之后,又设计了这款AD1955的解码器,AD1955的综合性能要优于CS4398,当然由低通模拟单元造成的成本也会大幅增加。

流程

本次设计,外观上采用了与上款439dac相同的机械外观尺寸,好处就是一旦做了外壳,可以通用。以下就整体设计展开详细描述。

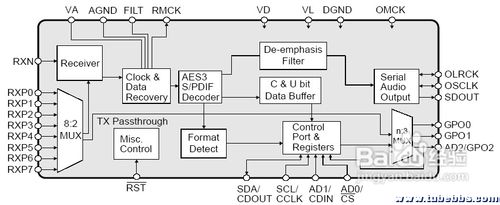

CS8416内部功能图

硬件模式下数据流程

硬件控制模式下的各引脚定义见表

确定CS8416的工作方式

引脚说明:

1脚:输入通道3

2脚:输入通道2

3脚:输入通道1

4脚:输入通道0

这4个输入通道的中不使用的通道可以悬浮或者直接接地处理,通道的选择由10脚和11脚的逻辑电平控制。可以输入单端信号或者差分信号。输入差分信号的时候需要与5脚配合。

5脚:差分输入的负端。当采用单端输入的时候,该引脚通过一个耦合电容接地。

6脚:VA。该脚为芯片内波模拟电路供电电源,该电源的精度则直接影响到时基抖动,对输出信号的稳定性造成影响。电压要求为3.3V

7脚:AGND。电源VA的模拟地。

8脚:锁相环滤波器接入脚。为了保证稳定性,滤波器RC网络的接地端一定要与7脚AGND尽可能短。

9脚:复位输入脚。低电平有效。

10脚:数据格式设定1

11脚:数据格式设定0

12脚:TX输出与RX通道直通选择设定1

13脚:TX输出与RX通道直通选择设定0

当TX不被使用的时候,请将TX通道设定到不被用到的输入通道上。

14脚:接收数据不能识别指示

15脚:音频数据流指示。

16脚:96KHZ采样频率检测。当采样频率小于等于48KHZ的时候,输出低电平;大于88.1KHZ的时候输出高电平。

17脚:数据接收器状态输出

18脚:U状态输出

19脚:C状态输出

20脚:TX输出引脚。

21脚:内部逻辑电路电源输入。电压为3.3V或者5V。

22脚:内部逻辑门电路电源地与内部音频数据处理单元电源地。

23脚:内部音频数据处理单元电源输入。电压为3.3V。

24脚:主时钟输出。

25脚:外部时钟输入。

26脚:串行音频数据流数据位输出。

27脚:串行音频数据流数据的位时钟输出。

28脚:串行音频数据流左右通道分割时钟输出。

AD1955的引脚图,对于不用的输入引脚(DSD数据输入端口),直接接地处理;不用的输出引脚(左右通道0标志输出引脚),悬浮处理;串行通讯口用上拉电阻接到电源即可。