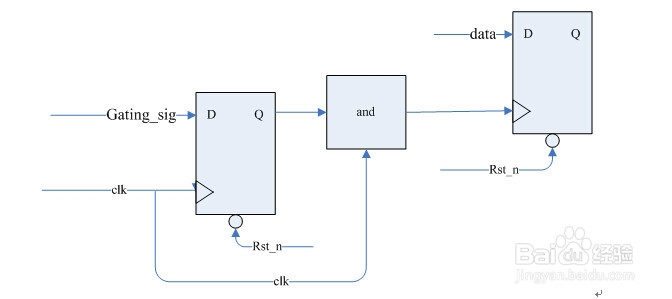

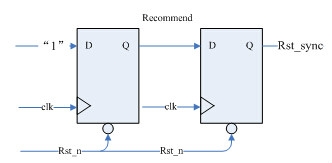

1、关于时钟(clk)和复位(rst_n),为了低功耗应当对时钟进行门控,复位信号应当采

用异步复位同步释放的方式。

2、 模块设计为总线类型接口,如果没有跨时钟域的问题则直接进行连接,如果有跨时钟域的问题需要针对性解决。

3、 系统集成时杜绝胶连逻辑(glue logic)

4、probe_pins用于调试时抓取内部的信号,譬如某个模块中比较关键的信号可以通过它进行芯片的调试

5、注意兼容性(如中断号的编排,register的安排,地址的mapping);注意re_use,最好做到只需要open或者close define

6、CSR(control state register)应该合理安排寄存器的位置,bit位等;SRAM要留有bist相关的信号