1、打开vivado,选择Create Project创建工程;弹出对话框后,点击Next。

2、Project Name对话框,填写工程名和工程存储位置,点击Next。

3、Project Type对话框,选择RTL Project,按需求选择Do not specify sources at this time;选择后添加源文件和约束文件将不会立即添加。

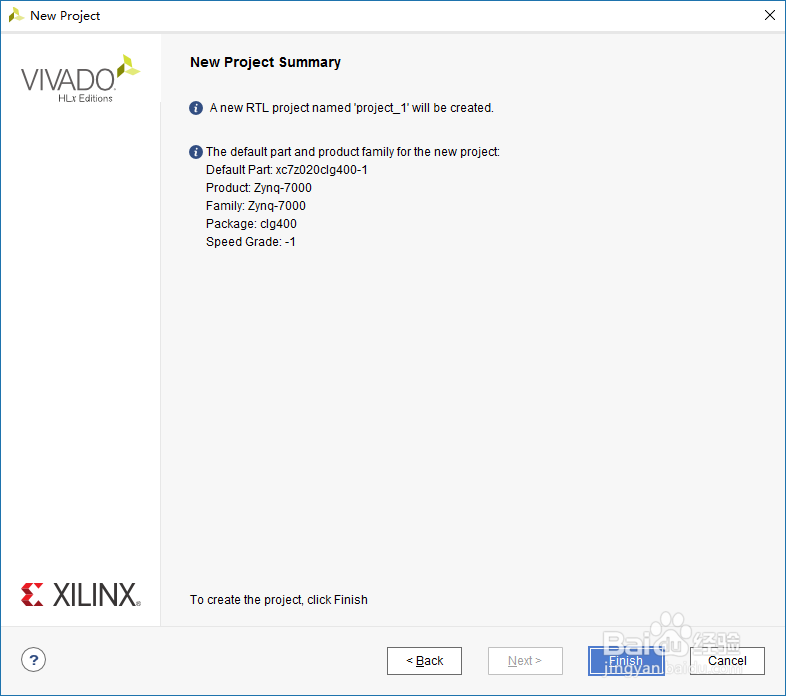

4、Default Part对话框,在搜索框中搜索需要的芯片型号,选择芯片,点击Next;New Project Summary对话框,选择Finish,进入工程界面。

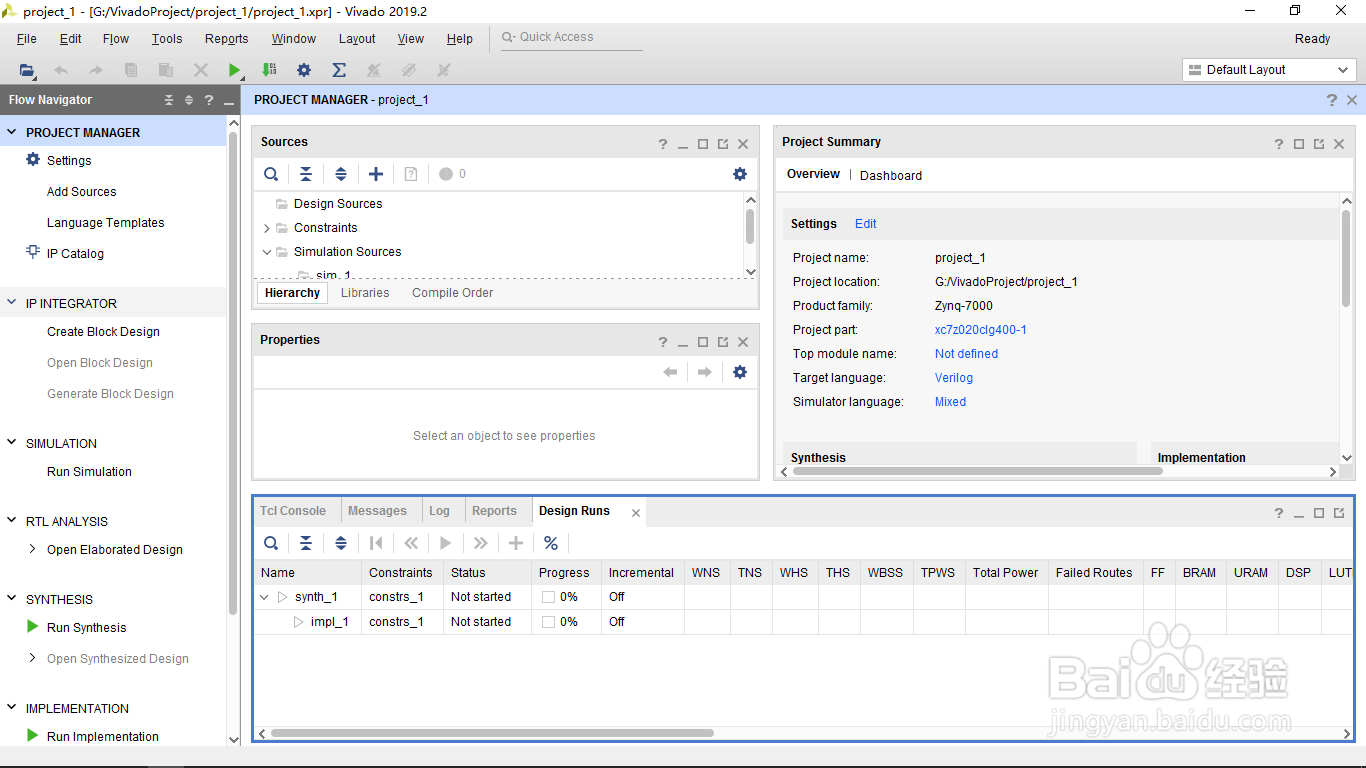

5、点击Add Sources,添加源文件和约束文件。

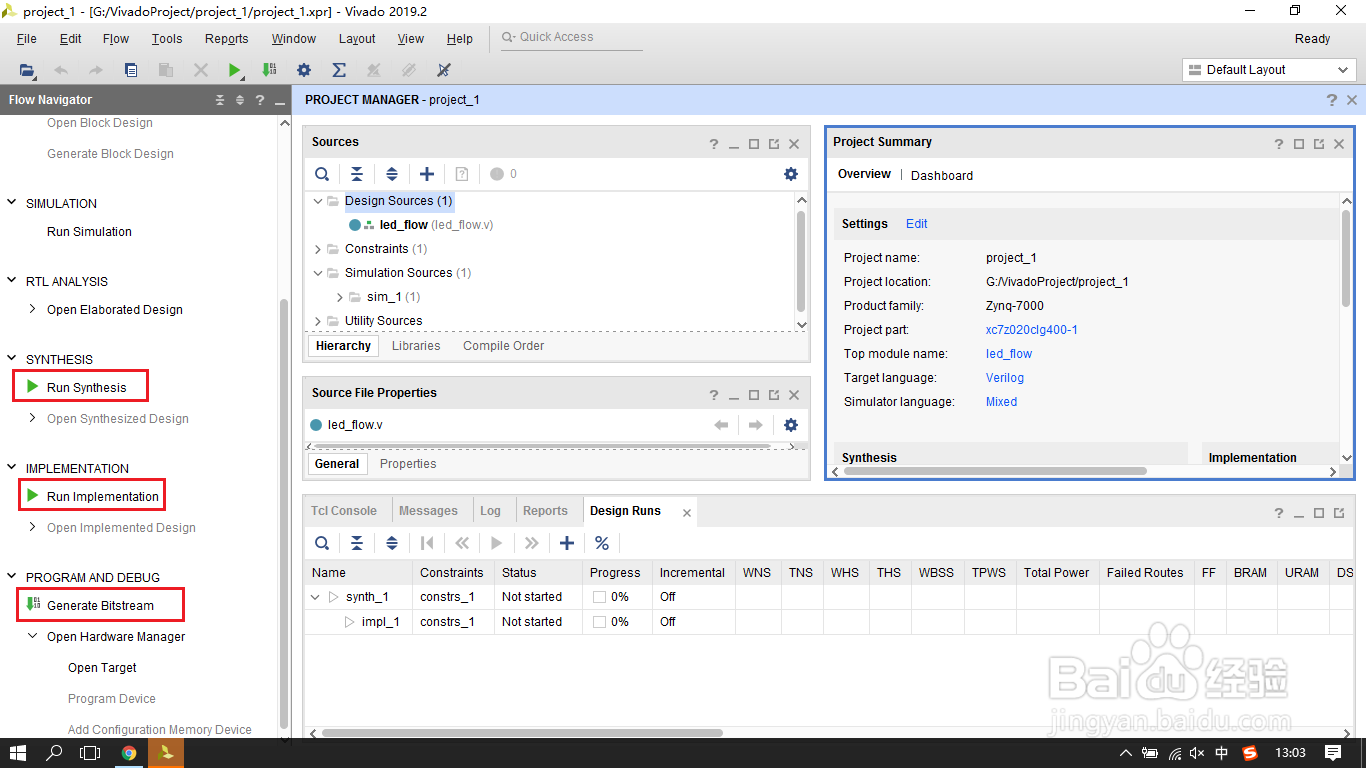

6、 在左侧的导航栏中,可以看到有三个选项,分别是:Synthesis (综合)、Implementation (实现)、Generate Bitstream (生成比特流)

这就是我们要进行的三步操作,点击Generate Bitstream,软件就会自动执行这三步操作,然后等待软件运行结束;

软件的右上角会显示当前运行的操作和运行状态,点击Cancel可以取消运行。

运行中检查出的错误提示信息和警告提示信息等,都会在下方的message栏里显示。

7、 生成比特流结束后会弹出一个对话框,选择 Open Hardware Manager ,打开硬件管理器,也可以在左侧导航列表中Generate Bitstream的下方点击打开。

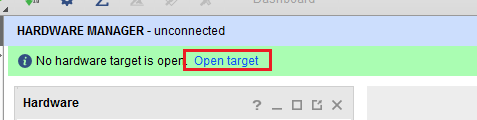

8、 打开硬件管理器后,需要连接好自己的FPGA开发板,然后点击 Open target ,这里可以直接选择 Auto Connect ,自动连接开发板

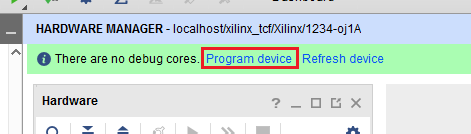

9、 连接开发板以后,会显示开发板的芯片型号以及当前是否被编程;点击上方的 Program device ,或在 Not programmed 处右键,选择 Program device ,会弹出一个编程窗口。

编程窗口中会自动选择当前工程生成的比特流文件,点击 Porgram ,就可以把程序下载到开发板上进行板级验证。