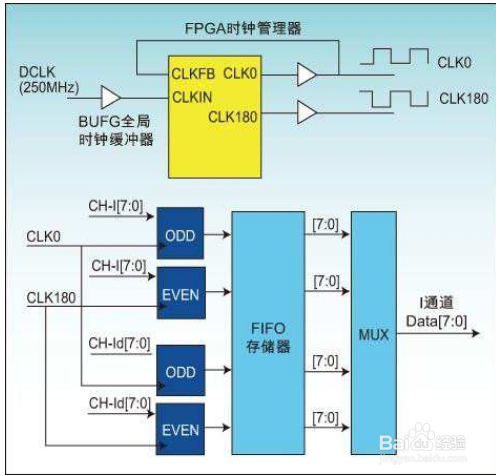

1、FPGA逻辑的速度一般跟不上高速转换器的总线速度,因此大多数FPGA具有串行器或解串器模块,用以将转换器端的快速。

2、针对总线中的每个数据位,此模块输出2和4或8位,但以二分之一和四分之一或者八分之一的时钟速率输出,从而有效地将数据解串。

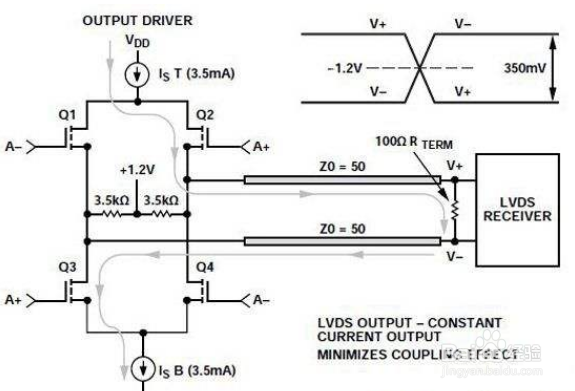

3、数据由FPGA内部的宽总线处理,其速度远低于连接到转换器的窄总线。但所需的线数则是CMOS的两倍,因而布线可能比较困难。

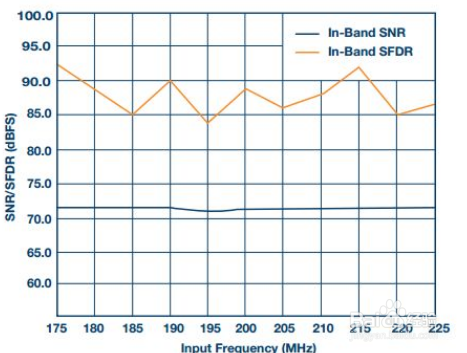

4、信号标准也用于串行链路,大部分是用在高速ADC上。当引脚数量比接口速度更重要时,通常使用串行。

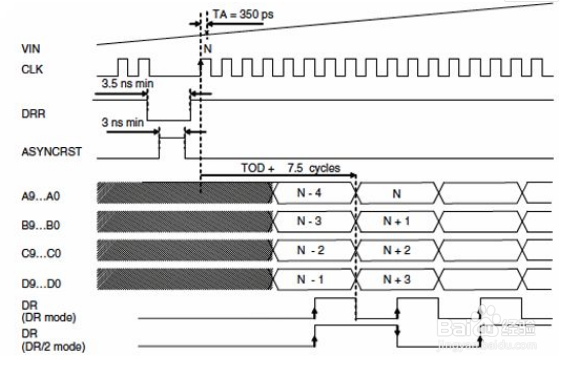

5、常常使用两个时钟:数据速率时钟和帧时钟。并行LVDS部分提到的所有考虑同样适用于串行LVDS。并行LVDS不过是由多条串行LVDS线组成。

6、可用片选线有多少,SPI就能支持多少器件。它的速度可达约100 赫兹,通常用作控制接口和数据接口。